Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture behaviour of rslatch is

signal q1, q2: std_logic;

begin

p_rslatch : process (r, s)

begin

if (q1 = 'U') or (q2 = 'U') then

q1 <= '1';

q2 <= '0';

q <= q1;

else

q1 <= r nor q2;

q2 <= s nor q1;

q <= q1;

end if;

end process;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

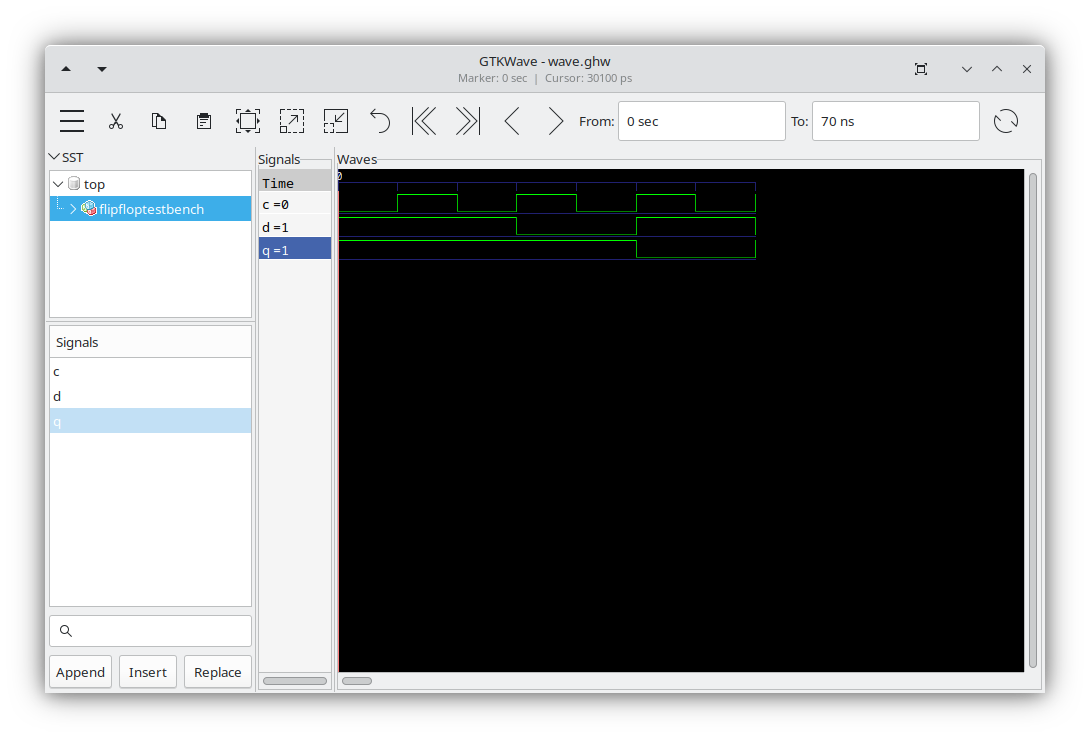

c <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns;

d <= '1' after 0 ns, '1' after 10 ns, '1' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns;

end;

Also, jetzt nicht verrückt machen lassen

1.) Das ist schon das MS Flip Flop. Das heisst, die Ausgabe erfolgt eine Taktflanke später, nämlich die fallende

2.) Die testbench ist nicht gut

2.1.) Ich brauche eine Wahrheitstabelle. Das bedeutet, ich muss mal entscheiden können, wie ich genau sehe, dass es geht

2.2.) das ist ein MS-Flip. Das heisst, Wirk und Kipperintervall überschneiden sich nicht

Das heisst nicht, dass es keine Setz und Haltezeit gibt. Es gibt in der Testbench ein Problem. Die Daten ändern sich, wenn sich der CLK ändert. Das ist nicht richtig, solange der sich ändert, muss es stabil sein.

OK, ich habe was am Programm geändert. Ich habe es ein Mal richtig geschrieben. das RS-Latch war schuld. Und ich habe es ein Mal richtig geschrieben, das habe ich jetzt wieder genommen

Jetzt war es falsch - weil. Ich habe Process verwendet. Das darf man nicht. Beim normalen VHDL, anders als bei C, werden die Anweisungen nicht hintereinander ausgeführt. Das ist logisch. Wenn etwas verschaltet ist, ist es parallel.

Trotzdem, kann man das mit Prozess Sequentiell machen. Das ist mir eigentlich klar. Nur heute war früh am Morgen und ich wollte das IF. Dann habe ich schnell zu Prozess gegriffen.

Das ist beim RS-Latch fehl am Platz. Ganz fehl am Platz. das RS-Latch lebt davon, dass es keinen Prozess gibt, sondern die so verschaltet sind. Davon lebt es

gegenfrage. Wie habe ich das damals gemacht? Mit Undefinied 'U'. Nein, es gibt ein einfaches Mittel - es gibt ja

'0' after 1 ns, '1' after 2 ns

und so weiter. Dann hat die Schaltung eine Initilalisierungsphase. Vor einer ns ist - init = '0'. Danach '1'. Wenn das so ist, machen wir IF, aber ohne Prozess

Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

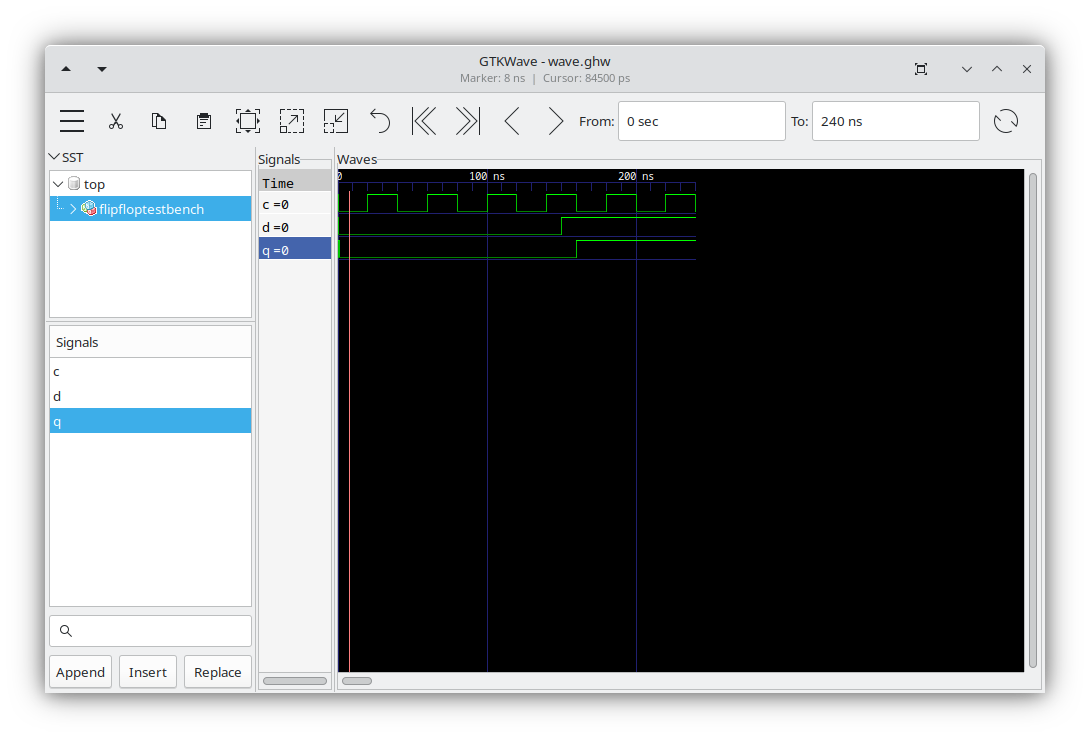

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns;

d <= '0' after 0 ns, '1' after 150 ns;

end;

Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

-- Die Testbench sieht gut aus

Es war halt früh am Morgen, es ist schon klar, dass ausgerechnet ein Latch kein Prozess sein kann, weil es eine Schaltung ist, wie sie ist

So, sieht die Testbench gut aus

Für alle Leute, die mich jetzt kritisieren, sei gesagt, das ist nicht schwer

1.) RS-Latch

2.) RS-Latch mit CLK eingang

3.) D-Latch

4.) D-MS-FF

5.) JK-MS-FF

Wie das letzte geht, weiss ich nicht auswendig

Sie müssen bei RS-Latch einfach lernen

Code: Alles auswählen

Q := R NOR Q'

Q' := S NOR Q

Code: Alles auswählen

S = A XOR B XOR C

U = A AND B OR A OR B AND C

Code: Alles auswählen

X NOR 0 = NOT X

X NOR 1 = 0

Dann mit CLK-Eingang. Wir haben Eingang R und S. Gut - und dann machen wir bei beiden einen AND zu einem CLK dazu

Dann D-Latch. Wir verbinden R und S invertiert

Und D-MS-FF. Wir nehmen zwei D-Latches. Und schalten die hintereinander, Q und D. Und machen den Takt Invertiert.

Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

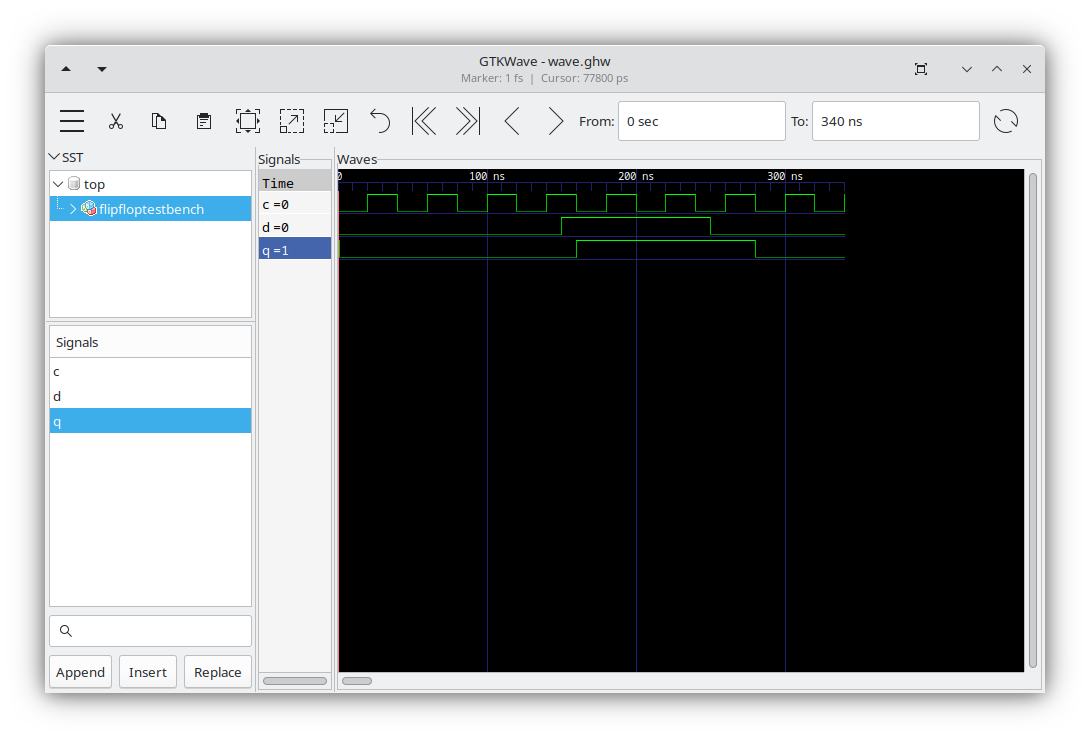

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns,

'1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d <= '0' after 0 ns, '1' after 150 ns, '0' after 250 ns;

end;

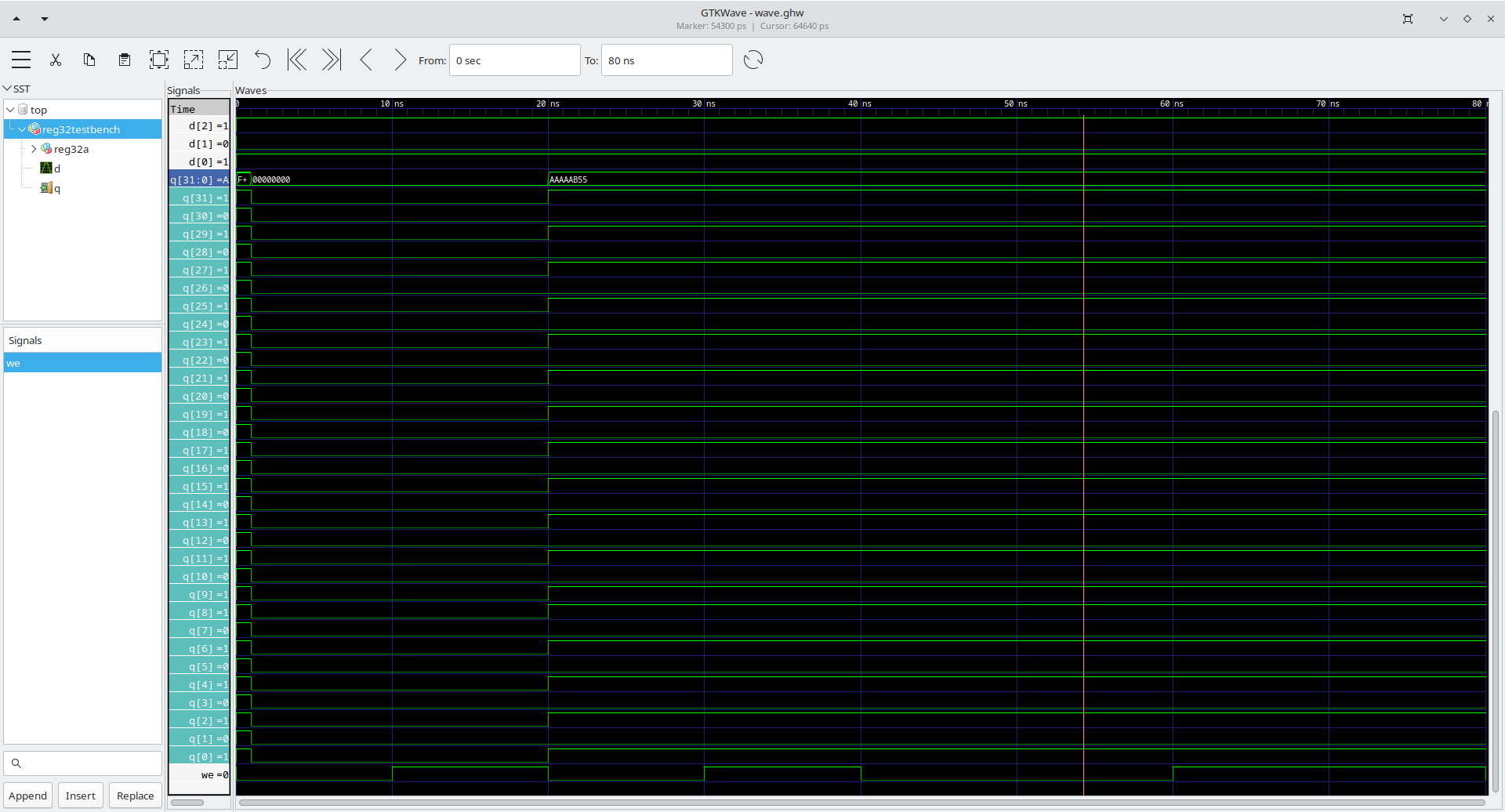

library ieee;

use ieee.std_logic_1164.all;

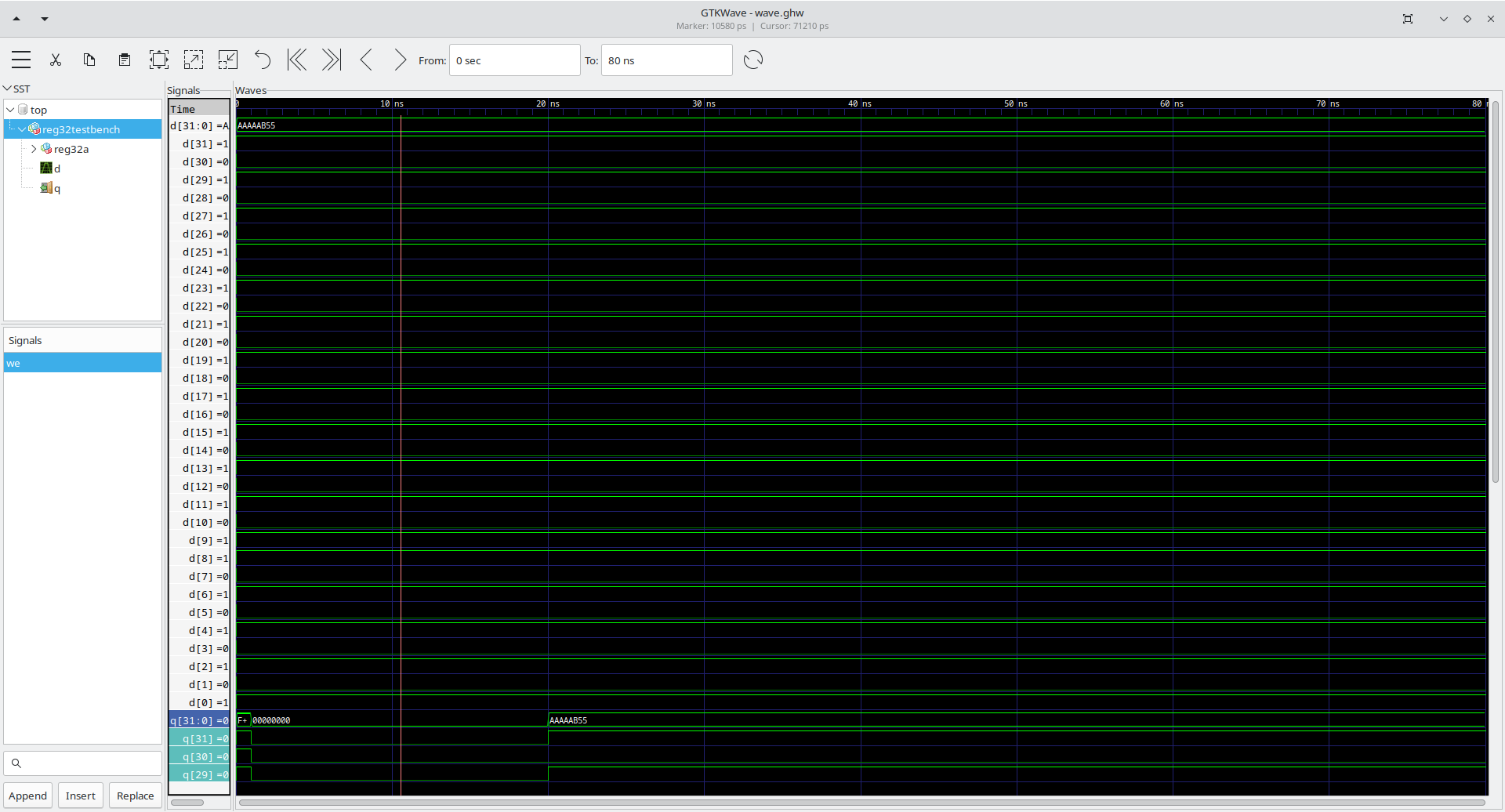

entity reg32 is

port (

we: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

dmsflipflop1: dmsflipflop PORT MAP (q=>q(i), d=>d(i), c=>we);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32testbench is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal we: std_logic;

begin

reg32a: reg32 PORT MAP (d=>d, q=>q, we=>we);

d(0) <= '1';

d(1) <= '0';

d(2) <= '1';

d(3) <= '0';

d(4) <= '1';

d(5) <= '0';

d(6) <= '1';

d(7) <= '0';

d(8) <= '1';

d(9) <= '1';

d(10) <= '0';

d(11) <= '1';

d(12) <= '0';

d(13) <= '1';

d(14) <= '0';

d(15) <= '1';

d(16) <= '0';

d(17) <= '1';

d(18) <= '0';

d(19) <= '1';

d(20) <= '0';

d(21) <= '1';

d(22) <= '0';

d(23) <= '1';

d(24) <= '0';

d(25) <= '1';

d(26) <= '0';

d(27) <= '1';

d(28) <= '0';

d(29) <= '1';

d(30) <= '0';

d(31) <= '1';

we <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns;

end;

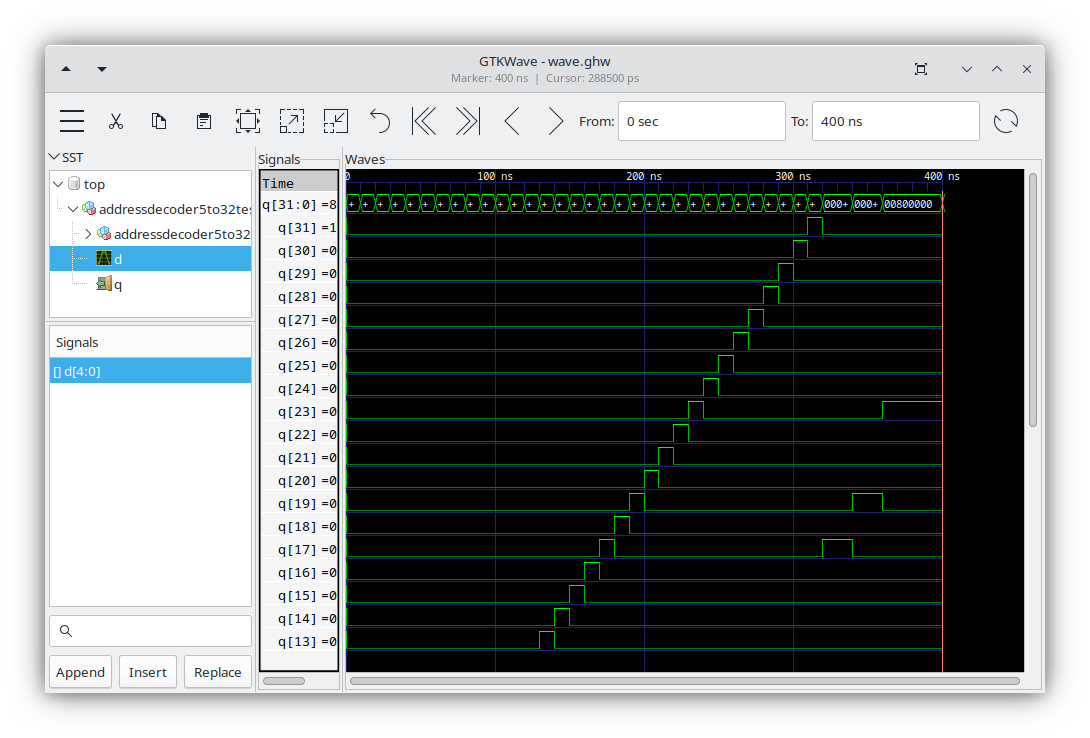

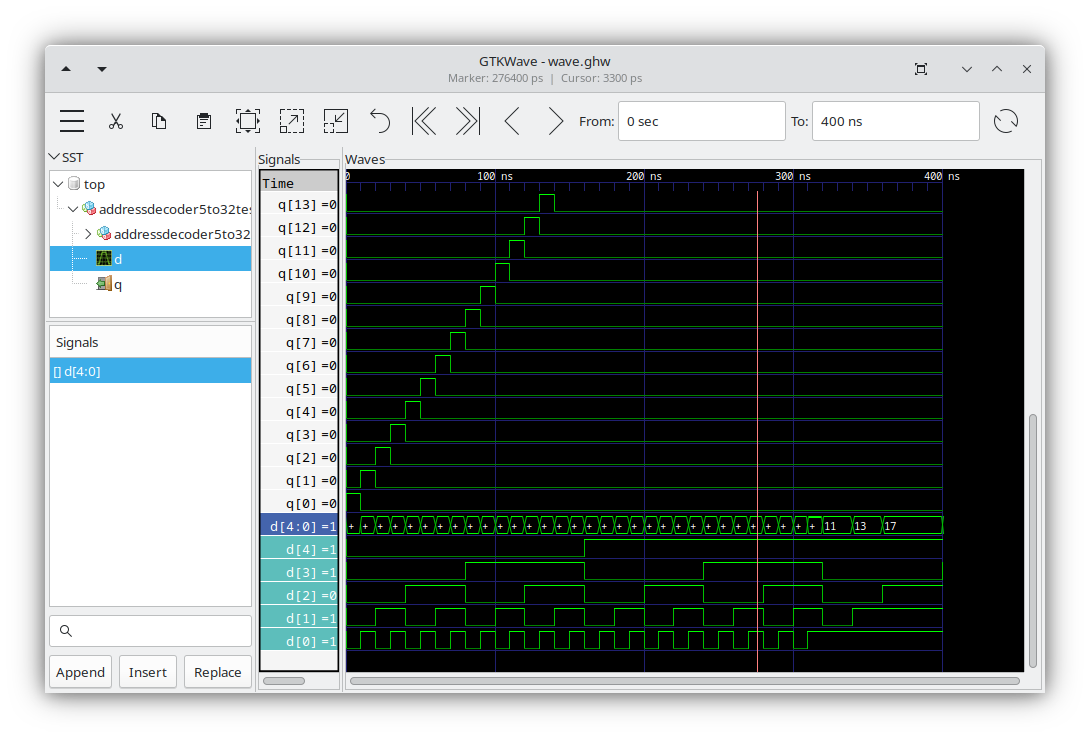

2 Leseregister Auswahl 5 Bit

1 Schreiberegister Auswahl 5 Bit

32 Bit 2x Leseport

32 Bit 1 Schreibport.

Mit WE - am Registerblock gibt es eine UND-Verknüpfung.

Jetzt machen wir als erstes für das Schreibe

- Schreiberegister - ein Dekoder. Addressdekoder, das führt zu jeweils 32 Registern

wir machen erst eine Entity und Architecture Componente - 32x32 Register-Block. Der enthält 32 x 32 Bit Register.

Code: Alles auswählen

// ein bisschen Coudle Moodle Bei der der Test Bench habe ich automatisch generiert. Aber das CM nur am Ende. Das macht nichts. Genügt für diesen Zweck. Ich habe das Addressdekodierer, zum Schreiben geschrieben und die Testbench automatisch mit diesem C Code generiert

#include <stdio.h>

int main (void) {

int i;

printf ("d (0) <= ");

for (i = 0; i < 30; i+=2) {

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns, ", (i+1) * 10);

}

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns;\n ", (i+1) * 10);

printf ("d (1) <= ");

for (i = 0; i < 30; i+=4) {

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns, ", (i+2) * 10);

}

printf ("'0' after %i ns;\n ", i * 10);

printf ("'1' after %i ns;\n ", (i+2) * 10);

printf ("d (2) <= ");

for (i = 0; i < 30; i+=8) {

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns, ", (i+4) * 10);

}

printf ("'0' after %i ns;\n ", i * 10);

printf ("'1' after %i ns;\n ", (i+4) * 10);

printf ("d (3) <= ");

for (i = 0; i < 30; i+=16) {

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns, ", (i+8) * 10);

}

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns;\n ", (i+8) * 10);

i = 0;

printf ("d (4) <= ");

printf ("'0' after %i ns, ", i * 10);

printf ("'1' after %i ns;\n ", (i+16) * 10);

return 0;

}Code: Alles auswählen

-- das ist das Ergebnis

d (0) <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns, '1' after 170 ns, '0' after 180 ns, '1' after 190 ns, '0' after 200 ns, '1' after 210 ns, '0' after 220 ns, '1' after 230 ns, '0' after 240 ns, '1' after 250 ns, '0' after 260 ns, '1' after 270 ns, '0' after 280 ns, '1' after 290 ns, '0' after 300 ns, '1' after 310 ns;

d (1) <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns, '0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns, '1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d (2) <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns, '1' after 120 ns, '0' after 160 ns, '1' after 200 ns, '0' after 240 ns, '1' after 280 ns, '0' after 320 ns, '1' after 360 ns;

d (3) <= '0' after 0 ns, '1' after 80 ns, '0' after 160 ns, '1' after 240 ns, '0' after 320 ns, '1' after 400 ns;

d (4) <= '0' after 0 ns, '1' after 160 ns;Code: Alles auswählen

-- Hier das Addressdekoder

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32 is

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32 is

begin

-- 00000

b (0) <= not a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 00001

b (1) <= not a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 00010

b (2) <= not a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 00011

b (3) <= not a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 00100

b (4) <= not a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 00101

b (5) <= not a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 00110

b (6) <= not a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 00111

b (7) <= not a (4) and not a (3) and a (2) and a (1) and a (0);

-- 01000

b (8) <= not a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 01001

b (9) <= not a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 01010

b (10) <= not a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 01011

b (11) <= not a (4) and a (3) and not a (2) and a (1) and a (0);

-- 01100

b (12) <= not a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 01101

b (13) <= not a (4) and a (3) and a (2) and not a (1) and a (0);

-- 01110

b (14) <= not a (4) and a (3) and a (2) and a (1) and not a (0);

-- 01111

b (15) <= not a (4) and a (3) and a (2) and a (1) and a (0);

-- 10000

b (16) <= a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 10001

b (17) <= a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 10010

b (18) <= a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 10011

b (19) <= a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 10100

b (20) <= a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 10101

b (21) <= a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 10110

b (22) <= a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 10111

b (23) <= a (4) and not a (3) and a (2) and a (1) and a (0);

-- 11000

b (24) <= a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 11001

b (25) <= a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 11010

b (26) <= a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 11011

b (27) <= a (4) and a (3) and not a (2) and a (1) and a (0);

-- 11100

b (28) <= a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 11101

b (29) <= a (4) and a (3) and a (2) and not a (1) and a (0);

-- 11110

b (30) <= a (4) and a (3) and a (2) and a (1) and not a (0);

-- 11111

b (31) <= a (4) and a (3) and a (2) and a (1) and a (0);

end;

Jetzt kommt an jedem der WE's der 32 Bit Register, das Addressdekoder, im Registerblock. Aber nicht so einfach. sondern UND verknüpft mit dem WE des Registerblocks.

Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns,

'1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d <= '0' after 0 ns, '1' after 150 ns, '0' after 250 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

we: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

dmsflipflop1: dmsflipflop PORT MAP (q=>q(i), d=>d(i), c=>we);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32testbench is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal we: std_logic;

begin

reg32a: reg32 PORT MAP (d=>d, q=>q, we=>we);

d(0) <= '1';

d(1) <= '0';

d(2) <= '1';

d(3) <= '0';

d(4) <= '1';

d(5) <= '0';

d(6) <= '1';

d(7) <= '0';

d(8) <= '1';

d(9) <= '1';

d(10) <= '0';

d(11) <= '1';

d(12) <= '0';

d(13) <= '1';

d(14) <= '0';

d(15) <= '1';

d(16) <= '0';

d(17) <= '1';

d(18) <= '0';

d(19) <= '1';

d(20) <= '0';

d(21) <= '1';

d(22) <= '0';

d(23) <= '1';

d(24) <= '0';

d(25) <= '1';

d(26) <= '0';

d(27) <= '1';

d(28) <= '0';

d(29) <= '1';

d(30) <= '0';

d(31) <= '1';

we <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32 is

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32 is

begin

-- 00000

b (0) <= not a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 00001

b (1) <= not a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 00010

b (2) <= not a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 00011

b (3) <= not a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 00100

b (4) <= not a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 00101

b (5) <= not a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 00110

b (6) <= not a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 00111

b (7) <= not a (4) and not a (3) and a (2) and a (1) and a (0);

-- 01000

b (8) <= not a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 01001

b (9) <= not a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 01010

b (10) <= not a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 01011

b (11) <= not a (4) and a (3) and not a (2) and a (1) and a (0);

-- 01100

b (12) <= not a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 01101

b (13) <= not a (4) and a (3) and a (2) and not a (1) and a (0);

-- 01110

b (14) <= not a (4) and a (3) and a (2) and a (1) and not a (0);

-- 01111

b (15) <= not a (4) and a (3) and a (2) and a (1) and a (0);

-- 10000

b (16) <= a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 10001

b (17) <= a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 10010

b (18) <= a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 10011

b (19) <= a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 10100

b (20) <= a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 10101

b (21) <= a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 10110

b (22) <= a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 10111

b (23) <= a (4) and not a (3) and a (2) and a (1) and a (0);

-- 11000

b (24) <= a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 11001

b (25) <= a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 11010

b (26) <= a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 11011

b (27) <= a (4) and a (3) and not a (2) and a (1) and a (0);

-- 11100

b (28) <= a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 11101

b (29) <= a (4) and a (3) and a (2) and not a (1) and a (0);

-- 11110

b (30) <= a (4) and a (3) and a (2) and a (1) and not a (0);

-- 11111

b (31) <= a (4) and a (3) and a (2) and a (1) and a (0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32testbench is

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (4 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (b=>q, a=>d);

d (0) <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns, '1' after 170 ns, '0' after 180 ns, '1' after 190 ns, '0' after 200 ns, '1' after 210 ns, '0' after 220 ns, '1' after 230 ns, '0' after 240 ns, '1' after 250 ns, '0' after 260 ns, '1' after 270 ns, '0' after 280 ns, '1' after 290 ns, '0' after 300 ns, '1' after 310 ns;

d (1) <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns, '0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns, '1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d (2) <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns, '1' after 120 ns, '0' after 160 ns, '1' after 200 ns, '0' after 240 ns, '1' after 280 ns, '0' after 320 ns, '1' after 360 ns;

d (3) <= '0' after 0 ns, '1' after 80 ns, '0' after 160 ns, '1' after 240 ns, '0' after 320 ns, '1' after 400 ns;

d (4) <= '0' after 0 ns, '1' after 160 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset32x32 is

port (

writereg: in std_logic_vector (4 downto 0);

readreg1: in std_logic_vector (4 downto 0);

readreg2: in std_logic_vector (4 downto 0);

readport1: out std_logic_vector (31 downto 0);

readport2: out std_logic_vector (31 downto 0);

writeport: in std_logic_vector (31 downto 0);

we: in std_logic

);

end;

architecture behaviour of registerset32x32 is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

begin

end;

Code: Alles auswählen

-- Jetzt mache ich Pause. Die Sache ist nicht vollstdändig. Ich habe Leseports ohne Multiplexer verbunden. das ist falsch . ich habe WARNING WARNING hintergeschrieben, da müssen Multiplexer hin

-- Ich mache aber Pause

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns,

'1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d <= '0' after 0 ns, '1' after 150 ns, '0' after 250 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

we: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

dmsflipflop1: dmsflipflop PORT MAP (q=>q(i), d=>d(i), c=>we);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32testbench is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal we: std_logic;

begin

reg32a: reg32 PORT MAP (d=>d, q=>q, we=>we);

d(0) <= '1';

d(1) <= '0';

d(2) <= '1';

d(3) <= '0';

d(4) <= '1';

d(5) <= '0';

d(6) <= '1';

d(7) <= '0';

d(8) <= '1';

d(9) <= '1';

d(10) <= '0';

d(11) <= '1';

d(12) <= '0';

d(13) <= '1';

d(14) <= '0';

d(15) <= '1';

d(16) <= '0';

d(17) <= '1';

d(18) <= '0';

d(19) <= '1';

d(20) <= '0';

d(21) <= '1';

d(22) <= '0';

d(23) <= '1';

d(24) <= '0';

d(25) <= '1';

d(26) <= '0';

d(27) <= '1';

d(28) <= '0';

d(29) <= '1';

d(30) <= '0';

d(31) <= '1';

we <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32 is

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32 is

begin

-- 00000

b (0) <= not a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 00001

b (1) <= not a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 00010

b (2) <= not a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 00011

b (3) <= not a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 00100

b (4) <= not a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 00101

b (5) <= not a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 00110

b (6) <= not a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 00111

b (7) <= not a (4) and not a (3) and a (2) and a (1) and a (0);

-- 01000

b (8) <= not a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 01001

b (9) <= not a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 01010

b (10) <= not a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 01011

b (11) <= not a (4) and a (3) and not a (2) and a (1) and a (0);

-- 01100

b (12) <= not a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 01101

b (13) <= not a (4) and a (3) and a (2) and not a (1) and a (0);

-- 01110

b (14) <= not a (4) and a (3) and a (2) and a (1) and not a (0);

-- 01111

b (15) <= not a (4) and a (3) and a (2) and a (1) and a (0);

-- 10000

b (16) <= a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 10001

b (17) <= a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 10010

b (18) <= a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 10011

b (19) <= a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 10100

b (20) <= a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 10101

b (21) <= a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 10110

b (22) <= a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 10111

b (23) <= a (4) and not a (3) and a (2) and a (1) and a (0);

-- 11000

b (24) <= a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 11001

b (25) <= a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 11010

b (26) <= a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 11011

b (27) <= a (4) and a (3) and not a (2) and a (1) and a (0);

-- 11100

b (28) <= a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 11101

b (29) <= a (4) and a (3) and a (2) and not a (1) and a (0);

-- 11110

b (30) <= a (4) and a (3) and a (2) and a (1) and not a (0);

-- 11111

b (31) <= a (4) and a (3) and a (2) and a (1) and a (0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32testbench is

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (4 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (b=>q, a=>d);

d (0) <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns, '1' after 170 ns, '0' after 180 ns, '1' after 190 ns, '0' after 200 ns, '1' after 210 ns, '0' after 220 ns, '1' after 230 ns, '0' after 240 ns, '1' after 250 ns, '0' after 260 ns, '1' after 270 ns, '0' after 280 ns, '1' after 290 ns, '0' after 300 ns, '1' after 310 ns;

d (1) <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns, '0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns, '1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d (2) <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns, '1' after 120 ns, '0' after 160 ns, '1' after 200 ns, '0' after 240 ns, '1' after 280 ns, '0' after 320 ns, '1' after 360 ns;

d (3) <= '0' after 0 ns, '1' after 80 ns, '0' after 160 ns, '1' after 240 ns, '0' after 320 ns, '1' after 400 ns;

d (4) <= '0' after 0 ns, '1' after 160 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset32x32 is

port (

writereg: in std_logic_vector (4 downto 0);

readreg1: in std_logic_vector (4 downto 0);

readreg2: in std_logic_vector (4 downto 0);

readport1: out std_logic_vector (31 downto 0);

readport2: out std_logic_vector (31 downto 0);

writeport: in std_logic_vector (31 downto 0);

we: in std_logic

);

end;

architecture behaviour of registerset32x32 is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal writereg1: std_logic_vector (31 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (a=>writereg, b=>writereg1);

l1:

for i in 0 to 31 generate

reg32a: reg32 PORT MAP (we=>writereg1(i),d=>writeport,q=>readport1); -- WARNING - WARNING

end generate;

end;